Parallel Input Serial Output Shift Register Vhdl Code Rating: 4,5/5 9115 reviews

- Parallel Input Serial Output Shift Registers

- 4-bit Shift Register Vhdl Code

- Serial Input Serial Output Shift Register

Design of Parallel In - Serial OUT Shift Register using Behavior Modeling Style -

Par2ser.vhd par2ser Parallel to Serial. -- Implements a simple loadable register in VHDL. The IFDX D-type flip-flop is contained in an input/output.

- Jul 17, 2013. Parallel Out Shift Register using D-Flip Flop (VHDL Code). Parallel In - Serial OUT Shift Register. Design of Serial In - Parallel Out Shift.

- Vhdl and verilog codes. Right shift register; left shift register; parallel in parallel out (pipo) parallel in serial out (piso) serial in parallel out.

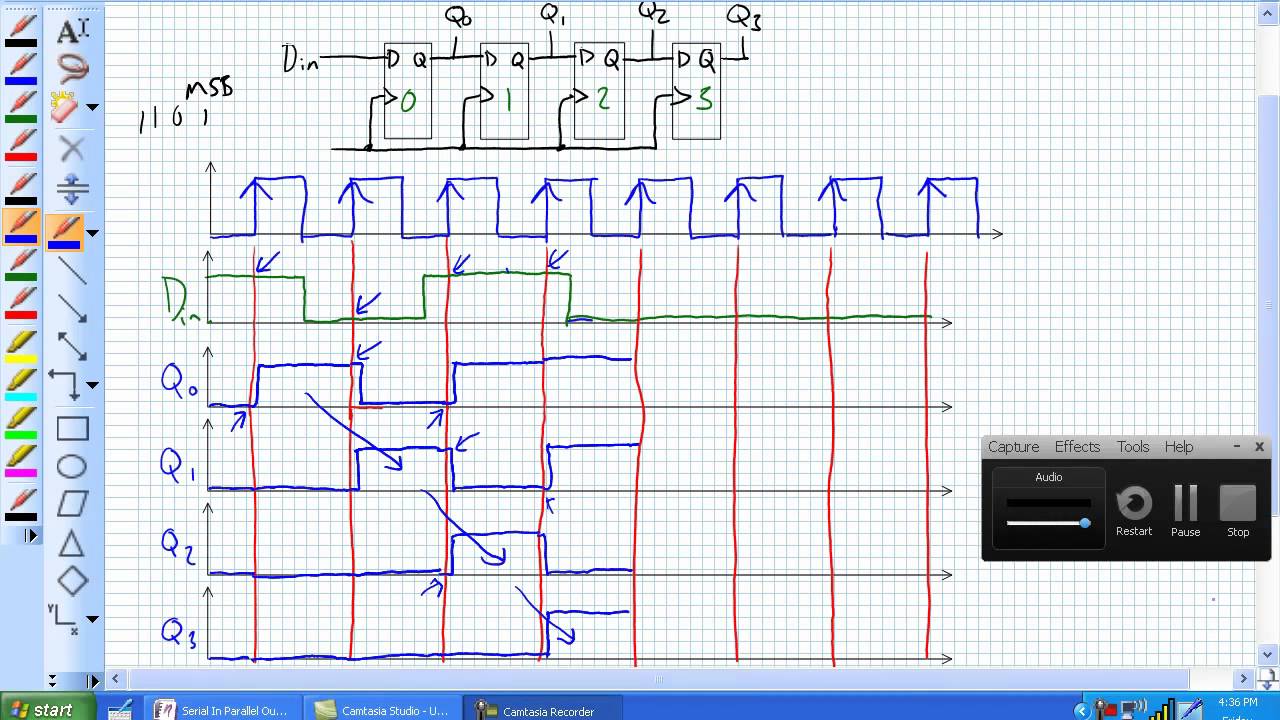

| Output Waveform : Parallel IN - Serial OUT Shift Register |

Verilog CODE -

//-----------------------------------------------------------------------------

//

// Title : parallel_in_serial_out

// Design : vhdl_upload2

// Author : Naresh Singh Dobal

// Company : nsdobal@gmail.com

Parallel Input Serial Output Shift Registers

// Verilog HDL Programs & Exercise with Naresh Singh Dobal.

//

//-----------------------------------------------------------------------------

//

// File : Parallel IN - Serial OUT Shift Register.v

module parallel_in_serial_out ( din ,clk ,reset ,load ,dout );

output dout ;

4-bit Shift Register Vhdl Code

reg dout ;input [3:0] din ;

wire [3:0] din ;

input clk ;

wire clk ;

input reset ;

wire reset ;

input load ;

wire load ;

reg [3:0]temp;

always @ (posedge (clk)) begin

if (reset)

temp <= 1;

else if (load)

temp <= din;

else begin

dout <= temp[3];

temp <= {temp[2:0],1'b0};

Serial Input Serial Output Shift Register

end

end

endmodule